# Delay Analysis in HCMOS Logic ICs by Widianto Widianto

Submission date: 19-May-2023 08:47AM (UTC+0700) Submission ID: 2096689220 File name: 5.0094353.pdf (565.86K) Word count: 2868 Character count: 11266

### **Delay analysis in HCMOS logic ICs**

Cite as: AIP Conference Proceedings 2453, 020059 (2022); https://doi.org/10.1063/5.0094353 Published Online: 25 July 2022

Widianto and Robert Lis

AIP Author Services

## **English Language Editing** High-quality assistance from subject specialists

LEARN MORE

AIP Conference Proceedings 2453, 020059 (2022); https://doi.org/10.1063/5.0094353 © 2022 Author(s).

**2453**, 020059

#### **Delay Analysis in HCMOS Logic ICs**

Widianto<sup>1,a)</sup>, Robert Lis<sup>2)</sup>

<sup>1</sup>Department of Electrical Engineering, University of Muhammadiyah Malang, Malang, Indonesia <sup>2</sup>Department of Electrical Power Engineering, Wroclaw University of Science and Technology, Wroclaw, Poland

Corresponding Author: a)widianto@umm.ac.id

Abstract. Open defects may occur at interconnection between gates inside HCMOS logic ICs due to open metal at imperfect fabrication process affecting speed responses of the ICs. A SPICE simulation is thus proposed to analyze delays due to the defects inside the ICs. The ICs are designed from a HCMOS netlist library distributed by Nexperia Co. Ltd. Simulation results indicate that the delays linearly increase along with sizes and locations of the defects.

#### INTRODUCTION

A HCMOS (High-Speed Complementary Metal Oxide Semiconductor) logic IC (Integrated Circuit) is regarded under a family of CMOS ICs [1]. Thus, it is made of p-type and n-type MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) [2], with a higher speed response than that in the CMOS ICs.

There are six masks in fabrication process of the HCMOS IC, which are: n-well, polysilicon, n+ diffusion, p+ diffusion, contact, and metal [3], specifying the proper placement of the transistor by layout designed rules [4] describing the scalable width and spacing for each step of the masks.

The HCMOS IC contains a logic diagram where some logic gates are connected to each other for specific function [5]. For instance, an inverter IC consists of the three inverter gates where the output gate one is connected to the other input gate and so on. The metal of the masks is utilized to connect each logic gate to others [6]. Construction of the parallel metal layer forms the capacitor with low capacitance values [7]. However, resistor is formed by series of metal layers along with resistance values depending on resistivity of the layer.

An open defect might thus occur at interconnection between logic gates [8] due to the open metal at the imperfect fabrication process. Moreover, the open defect in the metal might linearly increase along with the resistance values of the metal and the speed response of the IC.

The open defect between logic gates inside an IC was detected by an IDDQ testing [9], indicating that a large quiescent supply current will flow when the open defect occurs inside it. However, an ESD (Electronic Discharge) circuit should be added in each input gate requiring large space.

Delay testing is proposed to detect the open defects [10]. However, a test pattern should be prepared prior to testing logic IC one, requiring longer preparation time for different test patterns.

This study proposes a SPICE (Simulation Program with Integrated Circuit Emphasis) simulation of LTSpiceXVII to analyze delays in HCMOS logic gate ICs due to open defects. The ICs are designed by a HCMOS netlist library distributed by Nexperia Co. Ltd. The simulations results indicate that the delays in the IC are analyzed where the delay linearly increase along with sizes and locations of the defects.

#### METHODS

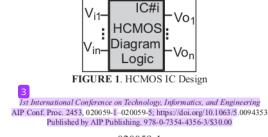

A HCMOS logic IC consists of a logic diagram with input voltages of Vi1 to Vin, and output voltages of Vo1 to Von, depicted in Figure 1. The diagram presents different specific functions of the IC, which include: Inverter, NOR, and NAND as well as other logic gates, such as: an inverter logic IC constructed by the three inverter logic gates.

Open defects occur at each input gate inside HCMOS logic ICs. For example, a logic diagram of an inverter logic IC is illustrated in Figure 2. As previously illustrated in Figure 1, the inverter IC has an input voltage of Vi and an output voltage of Vo. The open defect occurs inside the IC: a, b, and c nodes.

FIGURE 2. Inverter logic diagram

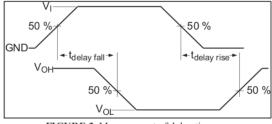

In the logic ICs, the defect generates the delays derived by providing stimulus signals to the IC inputs and by measuring time intervals between generated signals at IC outputs and its stimulus. The delays are divided into two types, which include: delay fall time *tdelayf* and delay rise time *tdelayf*.

The delay measurement of the inverter IC is illustrated in Figure 3, measured to time interval between generated signal waveform at *Vo* and stimulus signal waveform at *Vi*. As illustrated in Figure 1, *tdelayf* is measured to time interval between the move waveform from high level to low level signal reaching 50% at *Vo* and the move waveform from high level to low level signal reaching 50% at *Vo* and the move waveform from high level to low level signal reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from low level to high level reaches 50% at *Vo* and the move waveform from level to high level reaches 50% at *Vo* and th

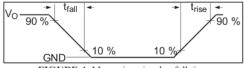

Moreover, the defect might increase fall time *tfall* and rise time *trise* at generated signals of IC outputs. *tfall* measures time interval of the move waveform from high to low level signal. On the other hand, *trise* measures time interval of the move waveform from low to high level signal.

FIGURE 3. Measurement of delay time

Measuring *tfall* and *trise* of the inverter IC is illustrated in Figure 4. As illustrated in Figure 4, *tfall* presents time interval of the move waveform from 90% high to 10% low level signal. However, time interval of the move waveform from 10% low to 90% high signal is presented by *trise*.

FIGURE 4. Measuring rise dan fall time

SPICE contains the facilities to measure *tdelayf*, *tdelayr*, *tfall*, and *trise* in the HCMOS logic IC design by applying a command '.meas'. The delays are triggered *trig* at *Vi* and targeted *targ* at *Vo*. Syntaxes for measurement are illustrated in Figure 5.

.meas tdelayr trig V(Vil to Vin) =  $0.5^{*}$ (Vil to Vin) fall = count targ V(V ol to V on) =  $0.5^{*}$ (V ol to V on) rise = count .meas tdelayr trig V(Vil to Vin) =  $0.5^{*}$ (V il to V in) fall = count targ V(V ol to V on) =  $0.5^{*}$ (V ol to V on) rise = count .meas trise trig V(V ol to V on) =  $0.1^{*}$ (V ol to V on) rise = count targ V(V ol to V on) =  $0.9^{*}$ (V ol to V on) rise = count .meas tfall trig V(V ol to V on) =  $0.9^{*}$ (V ol to V on) fall = count targ V(V ol to V on) =  $0.1^{*}$ (V ol to V on) fall = count

FIGURE 5. Syntaxes for measuring delay time

020059-2

#### RESULTS AND DISCUSSION

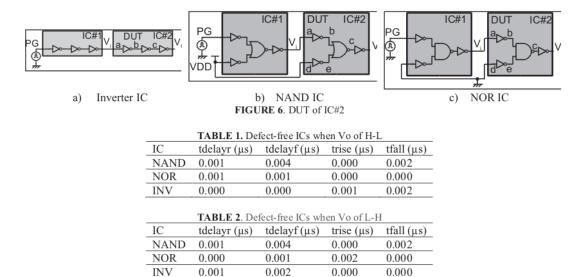

This study analyzes the HCMOS logic ICs, NAND, and NOR By creating the simulation circuits due to open defects in the HCMOS logic ICs. The circuits of inverter, NAND, and NOR are illustrated in Figure 6a, 6b, and 6c respectively. Each the Figure consists of two ICs, IC#1 and IC#2. A PG (Pattern Generator) is provided to IC#1. IC#2 as a DUT (Design Under Test) which the delays are measured.

The inverter IC has three targeted open defects of a, b, and c. Moreover, the NOR and NAND ICs have five targeted defects, located at a, b, c, d, and e nodes. Resistors *Ropen* of 1 k $\Omega$ , 10 k $\Omega$ , 100k, 1 M $\Omega$ , 10 M $\Omega$  are inserted to the targeted defects. The delays are measured to time interval between generated signal waveform at output voltage *Vo* and stimulus signal waveform at input voltage *Vi*. The measured delays include *tdelayr* and *tdelayf* along with measuring *trise* and *tfall*.

Simulation results of defect-free ICs when signals moving from high to low (H-L) at Vo are summarized in Table 1. Moreover, Table 2 summarizes simulation results of defect-free ICs when signals move from low to high (L-H) at Vo.

Simulation results of defective ICs where Ropen is inserted to the located defects are summarized in Table 3 and 4. Table 3 summarizes the results at Vo of H-L, while the results at Vo of L-H are summarized in Table 4.

| <b>TABLE 3.</b> Defective ICs at Vo of H-L |              |              |       |              |       |       |            |       |       |            |       |       |       |

|--------------------------------------------|--------------|--------------|-------|--------------|-------|-------|------------|-------|-------|------------|-------|-------|-------|

| Location                                   | Ropen<br>(Ω) | tdelayr (µs) |       | tdelayf (µs) |       |       | trise (µs) |       |       | tfall (µs) |       |       |       |

|                                            |              | NAND         | NOR   | INV          | NAND  | NOR   | INV        | NAND  | NOR   | INV        | NAND  | NOR   | INV   |

| b .                                        | 1 k          | 0.001        | 0.001 | 0.002        | 0.005 | 0.001 | 0.002      | 0.000 | 0.000 | 0.000      | 0.002 | 0.002 | 0.000 |

|                                            | 10 k         | 0.003        | 0.004 | 0.007        | 0.009 | 0.002 | 0.006      | 0.000 | 0.000 | 0.001      | 0.001 | 0.000 | 0.000 |

|                                            | 100 k        | 0.022        | 0.025 | 0.058        | 0.055 | 0.001 | 0.044      | 0.002 | 0.002 | 0.004      | 0.003 | 0.002 | 0.002 |

|                                            | 1 M          | 0.192        | 0.229 | 0.563        | 0.495 | 0.001 | 0.405      | 0.013 | 0.013 | 0.023      | 0.013 | 0.001 | 0.015 |

|                                            | 10 M         | 1.869        | 2.246 | 5.591        | 4.222 | 0.001 | 1.904      | 0.085 | 0.093 | 0.173      | 0.099 | 0.001 | 0.165 |

| a                                          | 1 k          | 0.001        | 0.001 | 0.001        | 0.005 | 0.002 | 0.002      | 0.000 | 0.000 | 0.000      | 0.001 | 0.001 | 0.000 |

|                                            | 10 k         | 0.005        | 0.005 | 0.003        | 0.011 | 0.002 | 0.003      | 0.000 | 0.000 | 0.000      | 0.001 | 0.000 | 0.000 |

|                                            | 100 k        | 0.041        | 0.041 | 0.015        | 0.063 | 0.002 | 0.017      | 0.000 | 0.001 | 0.000      | 0.001 | 0.000 | 0.000 |

|                                            | 1 M          | 0.387        | 0.392 | 0.119        | 0.582 | 0.002 | 0.141      | 0.003 | 0.002 | 0.001      | 0.002 | 0.000 | 0.001 |

|            | Ropen<br>(Ω)       | tdelayr (µs) |       | tdelayf (µs) |        |       | trise (µs) |       |       | tfall (µs) |       |       |       |

|------------|--------------------|--------------|-------|--------------|--------|-------|------------|-------|-------|------------|-------|-------|-------|

| Location _ |                    | NAND         | NOR   | INV          | NAND   | NOR   | INV        | NAND  | NOR   | INV        | NAND  | NOR   | INV   |

|            | 10 M               | 3.833        | 3.874 | 1.125        | 3.250  | 0.002 | 1.355      | 0.017 | 0.010 | 0.003      | 0.008 | 0.000 | 0.003 |

| _          | 1 k                | 0.001        | 0.002 | 0.002        | 0.005  | 0.002 | 0.003      | 0.001 | 0.001 | 0.001      | 0.002 | 0.001 | 0.001 |

| _          | 10 k               | 0.010        | 0.011 | 0.011        | 0.020  | 0.017 | 0.018      | 0.008 | 0.009 | 0.008      | 0.009 | 0.009 | 0.008 |

| c          | 100 k              | 0.100        | 0.100 | 0.101        | 0.169  | 0.167 | 0.168      | 0.083 | 0.085 | 0.083      | 0.089 | 0.084 | 0.087 |

| _          | 1 M                | 0.999        | 0.999 | 0.999        | 1.659  | 1.654 | 1.656      | 0.802 | 0.803 | 0.800      | 0.812 | 0.811 | 0.810 |

|            | 10 M               | 22.151       | ~     | 22.149       | 17.907 | ~     | 17.913     | ~     | ~     | ~          | ~     | ~     | ~     |

| _          | 1 k                | 0.001        | 0.001 |              | 0.005  | 0.001 |            | 0.000 | 0.000 |            | 0.001 | 0.001 |       |

| _          | 10 k               | 0.005        | 0.001 |              | 0.011  | 0.002 |            | 0.000 | 0.000 |            | 0.001 | 0.002 |       |

| d          | 4<br>100 k         | 0.041        | 0.036 |              | 0.064  | 0.002 |            | 0.000 | 0.000 |            | 0.001 | 0.002 |       |

| _          | 1 M                | 0.386        | 0.384 |              | 0.586  | 0.002 |            | 0.002 | 0.000 |            | 0.002 | 0.002 |       |

|            | 10 M               | 3.808        | 3.841 |              | 3.284  | 0.002 |            | 0.012 | 0.010 |            | 0.008 | 0.002 |       |

| _          | 1 k                | 0.001        | 0.001 |              | 0.005  | 0.001 |            | 0.000 | 0.000 |            | 0.002 | 0.002 |       |

| _          | 10 k               | 0.003        | 0.001 |              | 0.010  | 0.002 |            | 0.000 | 0.000 |            | 0.001 | 0.002 |       |

| e          | 100 <mark>k</mark> | 0.023        | 0.018 |              | 0.054  | 0.002 |            | 0.002 | 0.002 |            | 0.003 | 0.002 |       |

| _          | 1 M                | 0.206        | 0.207 |              | 0.484  | 0.002 |            | 0.013 | 0.013 |            | 0.015 | 0.002 |       |

|            | 10 M               | 2.013        | 2.078 |              | 4.150  | 0.002 |            | 0.088 | 0.086 |            | 0.136 | 0.002 |       |

| tfall (µs<br>NOR<br>01 0.000<br>02 0.002<br>03 0.000<br>13 0.000<br>09 0.000<br>01 0.000<br>01 0.000 | i)<br>INV<br>0.00<br>0.00<br>0.00<br>0.01<br>0.16<br>0.00                        |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 01 0.000<br>02 0.002<br>03 0.000<br>13 0.000<br>99 0.000<br>01 0.000                                 | 0.00<br>0.00<br>0.00<br>0.01<br>0.16                                             |

| 02 0.002   03 0.000   13 0.000   99 0.000   01 0.000                                                 | 0.00<br>0.00<br>0.01<br>0.16                                                     |

| 03 0.000   13 0.000   09 0.000   01 0.000                                                            | 0.00                                                                             |

| 13 0.000   99 0.000   01 0.000                                                                       | 0.01                                                                             |

| 0.000<br>01 0.000                                                                                    | 0.16                                                                             |

| 0.000                                                                                                |                                                                                  |

|                                                                                                      | 0.00                                                                             |

|                                                                                                      |                                                                                  |

| 0.000                                                                                                | 0.00                                                                             |

| 0.001                                                                                                | 0.00                                                                             |

| 0.000                                                                                                | 0.00                                                                             |

| 0.000 80                                                                                             | 0.00                                                                             |

| 0.001                                                                                                | 0.00                                                                             |

| 0.009                                                                                                | 0.00                                                                             |

| 39 0.086                                                                                             | 0.08                                                                             |

| L3 0.811                                                                                             | 0.81                                                                             |

| ~                                                                                                    | ~                                                                                |

| 0.002                                                                                                |                                                                                  |

| 0.002                                                                                                | _                                                                                |

|                                                                                                      | 02 0.000   08 0.000   02 0.001   09 0.009   89 0.086   13 0.811   7 ~   02 0.002 |

020059-4

| Location | Ropen | tdelayr (µs) |       | tde | elayf (µ | s)    | t   | rise (µs) |       | tfall (µs) |       |       |     |

|----------|-------|--------------|-------|-----|----------|-------|-----|-----------|-------|------------|-------|-------|-----|

| Location | (Ω)   | NAND         | NOR   | INV | NAND     | NOR   | INV | NAND      | NOR   | INV        | NAND  | NOR   | INV |

|          | 100 k | 0.041        | 0.039 |     | 0.064    | 0.002 |     | 0.000     | 0.000 |            | 0.001 | 0.002 |     |

|          | 1 M   | 0.386        | 0.387 |     | 0.586    | 0.002 |     | 0.002     | 0.002 |            | 0.002 | 0.001 |     |

|          | 10 M  | 1.739        | 1.774 |     | 5.776    | 0.002 |     | 0.012     | 0.010 |            | 0.009 | 0.001 |     |

|          | 1 k   | 0.001        | 0.001 |     | 0.005    | 0.001 |     | 0.000     | 0.000 |            | 0.001 | 0.002 |     |

|          | 10 k  | 0.003        | 0.002 |     | 0.010    | 0.002 |     | 0.000     | 0.000 |            | 0.003 | 0.002 |     |

| е        | 100 k | 0.023        | 0.020 |     | 0.054    | 0.002 |     | 0.002     | 0.002 |            | 0.003 | 0.002 |     |

|          | 1 M   | 0.206        | 0.192 |     | 0.484    | 0.002 |     | 0.014     | 0.012 |            | 0.015 | 0.000 |     |

|          | 10 M  | 1.326        | 1.325 |     | 4.739    | 0.002 |     | 0.098     | 0.093 |            | 0.136 | 0.002 |     |

#### CONCLUSIONS

A SPICE simulation was proposed in this study to analyze delays due to open defects at interconnection between gate inside HCMOS logic ICs. The measured delays are *tdelayr* and *tdelayf*, *trise* and *tfall*. The simulation results indicate that the delays linearly increase along with sizes and locations of the defects.

#### REFERENCES

- 1. R. J. Baker, CMOS: Circuit Design, Layout, and Simulation: Third Edition. (2011).

- S. S. Amrik Singh, "Evolution of CMOS Technology Past, Present and Future," International Journal of Engineering Research and Technology (IJERT), (2016).

- 3. J. Jessing, "CMOS fabrication," in The VLSI Handbook: Second Edition, (2016).

- 4. M. T. Bohr and I. A. Young, "CMOS Scaling Trends and beyond," IEEE Micro, (2017),

- 5. J. L. FUNK, "Electronics and Electronic Systems," in *Technology Change and the Rise of New Industries*, (2019).

6. R. Ritzenthaler *et al.*, "Diffusion and gate replacement: A new gate-first high-k/metal gate CMOS integration scheme suppressing gate height asymmetry," *IEEE Transactions on Electron Devices*, (2016),

- 7. B. Landgraf, "MOM Capacitance Measurements in a 130 nm CMOS Node," (2015).

- M. Andjelkovic, Z. Stamenkovic, M. Krstic, and R. Kraemer, "Impact of Resistive Open and Bridge Defects on the SET Robustness of Standard CMOS Combinational Logic," (2018).

- 9. N. Widianto, Lailis Syafaah, "IDDQ Testing For Detecting Resistive Open Defects Inhemos Logic ICS," in *SeminarNasionalTeknologi dan Rekayasa (SENTRA)*, 1–3 (2017).

- S. Pandey *et al.*, "SAT-ATPG Generated Multi-Pattern Scan Tests for Cell Internal Defects: Coverage Analysis for Resistive Opens and Shorts," (2020).

### Delay Analysis in HCMOS Logic ICs

#### ORIGINALITY REPORT

| 5<br>SIMILA | <b>%</b><br>ARITY INDEX                                         | 2%<br>INTERNET SOURCES                                                                                                        | 4%<br>PUBLICATIONS                                                               | 2%<br>STUDENT PAR                   | PERS |

|-------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------|------|

| PRIMAR      | Y SOURCES                                                       |                                                                                                                               |                                                                                  |                                     |      |

| 1           | Boulghas<br>Witulski. '<br>for combi<br>cmos tecl<br>great lake | er, Jeff Draper<br>soul, Sandeepa<br>'Critical charge<br>inational logic<br>hnology", Proc<br>es symposium<br>im on VLSI - Gl | an DasGupta,<br>e and set puls<br>in commercia<br>eedings of th<br>on Great lake | e widths<br>al 90nm<br>e 17th<br>es | 1 %  |

| 2           |                                                                 | d to Universita<br>versity of Sura                                                                                            | <u> </u>                                                                         | abaya The                           | 1%   |

| 3           | Suprianto                                                       | naril Sofi'i, Sudo<br>o. "Application<br><sup>F</sup> kaolin clay as<br>g, 2022                                               | of molecular                                                                     | dynamic                             | 1 %  |

| 4           | www.data                                                        | asheet.hk                                                                                                                     |                                                                                  |                                     | 1%   |

| 5           | Automati                                                        | Tian, Delin Jing<br>c Test Generat<br>of Systems bas                                                                          | ion Method f                                                                     | or                                  | 1 %  |

### and Model-Based Systems Engineering", Applied Sciences, 2022

Publication

Exclude quotes On Exclude bibliography On Exclude matches < 1%

# turnitin

### **Digital Receipt**

This receipt acknowledges that Turnitin received your paper. Below you will find the receipt information regarding your submission.

The first page of your submissions is displayed below.

| Submission author: | Widianto Widianto                    |

|--------------------|--------------------------------------|

| Assignment title:  | Publication Articles April-Juni 2023 |

| Submission title:  | Delay Analysis in HCMOS Logic ICs    |

| File name:         | 5.0094353.pdf                        |

| File size:         | 565.86K                              |

| Page count:        | 6                                    |

| Word count:        | 2,868                                |

| Character count:   | 11,266                               |

| Submission date:   | 19-May-2023 08:47AM (UTC+0700)       |

| Submission ID:     | 2096689220                           |

Copyright 2023 Turnitin. All rights reserved.