RESEARCH ARTICLE | MARCH 26 2024

## Detection of defective FinFET logic ICs by using FFTs **FREE**

W. Widianto 🖾 ; Robert Lis; Inda Rusdia Sofiani; La Febry Andira Rose Cynthia

() Check for updates

AIP Conf. Proc. 2927, 040034 (2024) https://doi.org/10.1063/5.0192094

# **APL Energy**

**Latest Articles Online!**

**Read Now**

## **Detection of Defective FinFET Logic ICs by Using FFTs**

W Widianto<sup>1a)</sup>, Robert Lis<sup>2)</sup>, Inda Rusdia Sofiani<sup>1)</sup>, La Febry Andira Rose Cynthia<sup>1)</sup>

<sup>1</sup>Department of Electrical Engineering, University of Muhammadiyah Malang, Malang, Indonesia <sup>2</sup>Department of Electrical Power Engineering, Wroclaw University of Science and Technology, Wroclaw, Poland

<sup>a)</sup>Corresponding author: widianto@umm.ac.id

Abstract. A FinFET (Fin Field Effect Transistor) is a non-planar transistor. It has a faster-switching speed, lower power consumption, and static leakage current than CMOSs (Complementary Metal Oxide Semiconductors), which are planar transistors. In the FinFET logic ICs (Integrated Circuits) fabrication process, open defects may occur at interconnects between gates inside them. Open metals may cause defects. Since the FinFET ICs may be operated in high-speed time, the defects are more difficult to analyze in time domain signals. There is a method of FFT (Fast Fourier Transform) computing signals converted from the time domain signals into frequency domain signals. Then, the derived frequency signals will be expressed into the function of the Fourier series. In this paper, the FFT analysis is proposed to detect the defects inside the ICs. The logic ICs of Buffer, AND, and OR are designed by a SPICE (Simulation Program with Integrated Circuit Emphasis) netlist library distributed by Nexperia Co. Ltd. Then, the defects are inserted inside the designed ICs and simulated using LTspice created by Analog Devices Inc. Simulation results show that magnitude signals of defective logic ICs in the Fourier series will decrease linearly with increasing sizes of the defects.

Keywords: FinFET logic ICs, Defective, FFT, SPICE.

#### **INTRODUCTION**

Development of ICs (Integrated Circuits) increased very fast. Sizes, performances, power requirements, and package densities are the main parameters of the circuits. Scaling of the circuits may affect improvements in process technology to make them. A FinFET (Fin Field Effect Transistor) technology may be found below 14 nm process nodes [1, 2]. There are some semiconductor foundries that utilized the technology, i.e., TSMC, Intel, Samsung, GlobalFoundires, and others.

The FinFET is a non-planar transistor [3]. It is made of P and N-types, which are composed of source, gate, and drain in each type. A transistor channel of the FinFET is constructed by a thin vertical fin with the gate wrapped fully around the channel and formed between the source and the drain [4]. Thus, the FinFET ICs have lower power consumption, faster-switching speed, and lower static leakage current than CMOS ICs, which are planar transistors.

In the fabrication process of the FinFET ICs, an open defect may occur at interconnect between logic gates inside them [5]. In the layout of the ICs, the defect may be caused by the open metal [6]. Since a metal may form resistance of the interconnects, thus size defects are equal to resistor values.

The open defect between logic gates inside an IC was detected by IDDQ testing [7]. Moreover, delay testing was proposed to detect the open defects [8, 9]. However, the defective ICs were still tested in time domain signals. Since the FinFET ICs may be operated at a high-speed time, so they are more difficult to be analyzed.

In order to simplify the signals analysis, they were evaluated in frequency domain signals by using FFTs [10]. The FFT may convert the signals from the time domains to the frequency domains and vice versa [11]. Thus, the FFT may be applicable to analyze signals generated by the FinFET ICs.

In this paper, the FFT analysis is proposed to detect the defects inside the ICs. The ICs are designed by a SPICE (Simulation Program with Integrated Circuit Emphasis) [12] netlist library distributed by Nexperia Co. Ltd [13].

2nd International Conference on Technology, Informatics, and Engineering AIP Conf. Proc. 2927, 040034-1–040034-5; https://doi.org/10.1063/5.0192094 Published under an exclusive license by AIP Publishing. 978-0-7354-4901-5/\$30.00 Then, they are simulated using LTspice created by Analog Devices Inc. Simulation results show that magnitude signals of defective ICs will decrease linearly with increasing sizes of the defects.

#### **METHODS**

In a FinFET logic IC, it consists of a logic diagram by input voltages *Vi*1 to *Vin* and output voltages *Vo*1 to *Von*. This is shown in **FIGURE 1**. The diagram makes different specific functions of the IC, for example, Buffer, OR, and AND. Moreover, the diagram is composed of some logic gates.

Open defects may occur at interconnects between logic gates inside the IC. The defective IC may be analyzed by measuring the signal generated by it in the output voltages. However, the common generated signals are domain time signals. In order to simplify the defects analysis, the domain time signals should be converted to domain frequency signals.

V<sub>i1</sub>– IC#i FinFET V<sub>in</sub>– Logic -Vo<sub>n</sub>

FIGURE 1. Logic Diagram of FinFET IC

An FFT is a method to compute signals converted from time domain signals into frequency domain signals. Then, the derived frequency signals will be expressed into the function of the Fourier series. There are common types of signal waveforms converted by the FFT, i.e., triangular, square, parabola, and full wave rectified sine.

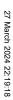

FIGURE 2. Signal Square Waveform

For example, the signal square waveform is illustrated in **FIGURE 2**. The waveform is defined in **Equation 1**. A fundamental frequency of the waveform is defined by **Equation 2**. The waveform is defined by the function of the Fourier series as denoted in **Equation 3**. However, the magnitude of the series will decay slowly as 1/n, where n is the number of points.

$$f(2\pi t) = h \text{ for } 0 \le 2\pi t \le \pi \text{ and } f(x) = 0 \text{ for } \pi \le 2\pi t \le 2\pi$$

$$(1)$$

$$f0 = \frac{1}{Tp}$$

(2)

$$f(2\pi t) = \frac{h}{2} + \frac{2h}{\pi} [\sin(2\pi t) + \frac{1}{3}\sin(6\pi t) + \frac{1}{5}\sin(10\pi t) + \frac{1}{7}\sin(14\pi t) + \cdots]$$

(3)

#### **RESULTS AND DISCUSSION**

In order to analyze FFTs in defective FinFET logic ICs, therefore Buffer, OR, and AND IC designs are proposed. They are designed by a SPICE netlist library distributed by Nexperia Co. Ltd. Moreover, they are simulated using the free SPICE simulator of LTspice created by Analog Devices.

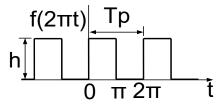

The defective FinFET IC designs are shown in **FIGURE 3**. The Buffer IC has three targeted open defects at interconnects between composed gates, i.e., *a*, *b*, and *c* nodes. Moreover, the OR and the AND ICs have three targeted defects located at the *a*, *b*, *c*, and *f* nodes. Resistors of 100  $\Omega$ , 1 k $\Omega$ , 1 M $\Omega$ , and 1 T $\Omega$  are inserted into the targeted defects.

A square waveform signal is provided to an input voltage Vi. As the waveform illustrated in **FIGURE 2**, an amplitude h and a time period Tp of Vi are 3 V and 2  $\mu$ s, respectively. VDD and GND are 3 V and 0 V, respectively. After inserting the resistor into the targeted defects, a generated signal of the ICs is measured in an output voltage Vo. The generated signal will be analyzed by using the FFT, which is facilitated by the LTspice.

FIGURE 3. FinFET logic IC Designs

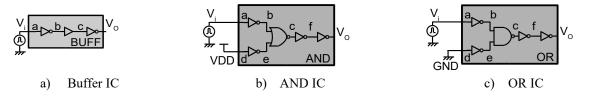

The FFT signal result of the defective Buffer IC by inserting the resistors of 100  $\Omega$ , 1 k $\Omega$ , and 1 M $\Omega$  to the targeted defects is shown in **FIGURE 4**. The result is represented by a function of the Fourier series as defined in Equation 3. Moreover, a fundamental frequency of the result is defined as Equation 2.

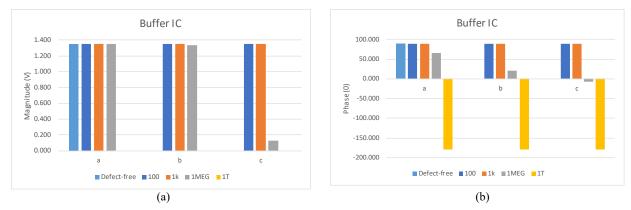

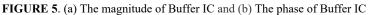

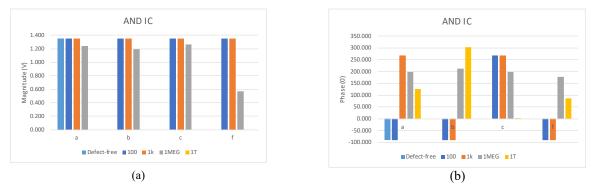

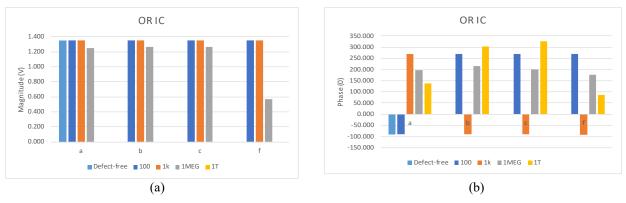

Furthermore, the FFT signal results of the defective Buffer, the NOR, and the AND ICs are charted in **FIGURES 5**, 6, and 7, respectively. As shown in **FIGURES 5a**, 6a, and 7a, the magnitudes of the function will decrease linearly with increasing the inserted resistor values.

Compared to delay testing results of open defects occurring at interconnects between gates inside ICs, the testing is derived from low-speed responses of the ICs in time domain signals[9]. Since measuring the delays is not facilitated by the LTspice, not like the FFT; thus the testing is not easy to analyze in high-speed responses.

FIGURE 4. FFT Result of Buffer FinFET IC

FIGURE 6. (a) The magnitude of AND IC and (b) The phase of AND IC

FIGURE 7. The magnitude of OR IC and (b) The phase of OR IC

### CONCLUSIONS

An FFT was proposed to analyze defective FinFET logic ICs caused by open defects occurring at interconnects between composed logic gates inside them. The proposed defective ICs are Buffer, AND, and OR ICs. The open defects are targeted by inserting resistors of  $100 \ \Omega - 1 \ T\Omega$  into the interconnects. The FFT results of the defective ICs will generate a function of the Fourier series. However, the magnitudes of the function will decrease linearly with increasing the inserted resistors.

#### REFERENCES

- N. E. I. Boukortt, T. R. Lenka, S. Patanè, and G. Crupi, "Effects of Varying the Fin Width, Fin Height, Gate Dielectric Material, and Gate Length on the DC and RF Performance of a 14-nm SOI FinFET Structure," *Electronics*, vol. 11, no. 1, 2022.

- [2] P. Oldiges et al., "Chip Power-Frequency Scaling in 10/7nm Node," *IEEE Access*, vol. 8, pp. 154329-154337, 2020.

- [3] S. K. Saha, FinFET devices for VLSI circuits and systems. CRC Press, 2020.

- [4] S. Kim et al., "Investigation of Device Performance for Fin Angle Optimization in FinFET and Gate-All-Around FETs for 3 nm-Node and Beyond," *IEEE Transactions on Electron Devices*, vol. 69, no. 4, pp. 2088-2093, 2022.

- [5] Y. Hashim, "The impact of channel fin width on electrical characteristics of Si-FinFET," *International Journal of Electrical and Computer Engineering*, vol. 12, no. 1, 2022.

- [6] F. Forero, J. M. Galliere, M. Renovell, and V. Champac, "A Semi-analytical Model for Interconnect Open Defects in FinFET Logic Cells," in 2019 IEEE Latin American Test Symposium (LATS), 2019, pp. 1-6.

- [7] J. Y. Liao, S. Rahimi, C. Schmidt, and H. L. Marks, "Failure Analysis of Total-Dose Radiation-Induced Degradation on FinFET Logic ICs," pp. 341-344: ASM International.

- [8] F. Forero, H. Villacorta, M. Renovell, and V. Champac, "Modeling and Detectability of Full Open Gate Defects in FinFET Technology," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 9, pp. 2180-2190, 2019.

- [9] Widianto and R. Lis, "Delay analysis in HCMOS logic ICs," *AIP Conference Proceedings*, vol. 2453, no. 1, p. 020059, 2022/07/25 2022, DOI: https://doi.org/10.1063/5.0094353.

- [10] S. Bailey et al., "A Mixed-Signal RISC-V Signal Analysis SoC Generator With a 16-nm FinFET Instance," IEEE Journal of Solid-State Circuits, vol. 54, no. 10, pp. 2786-2801, 2019.

- [11] Z. X. B. A. I. Y. C. X. Z. Y. Ma Liping, "An Accuracy Dynamically Configurable FFT Processor Based on Approximate Computing," *Journal of Shanghai Jiaotong University*, vol. 56, no. 2, pp. 223-230, 2022.

- [12] A. U. H. Pampori, S. A. Ahsan, and Y. S. Chauhan, "Modeling the Impact of Dynamic Fin-Width on the <italic>I</italic>&#x2013; <italic>V</italic>, <italic>C</italic>&#x2013; <italic>V</italic> and RF Characteristics of GaN Fin–HEMTs," *IEEE Transactions on Electron Devices*, vol. 69, no. 5, pp. 2275-2281, 2022.

- [13] M. Sarkar, S. T. Nasir, I. Chakraborty, S. Maity, R. Chakraborty, and G. S. Taki, "Performance Analysis of Various FINFET Threshold Logic based Full Adder Design," in 2019 3rd International Conference on Electronics, Materials Engineering & Nano-Technology (IEMENTech), 2019, pp. 1-5.