# Effects of Process Variations in a HCMOS IC using a Monte Carlo SPICE Simulation

by Artikel 2

**Submission date:** 17-Jan-2024 11:10AM (UTC+0700)

**Submission ID:** 2272326819

File name: Effects\_of\_Process\_Variations\_in\_a\_HCMOS\_IC\_using\_a\_Monte.pdf (442.13K)

Word count: 2077 Character count: 9945 Effects of Process Variations in a HCMOS IC using a Monte

11

### Carlo SPICE Simulation

Widianto\*1, Lailis Syafaah2, Nurhadi3 1,2,3Universitas Muhammadiyah Malang widianto@umm.ac.id\*

#### Abstract

In this paper, the effects of process variations in a HCMOS (High-Speed Complete Intary Metal Oxide Semiconductor) IC (Integrated Circuit) are examined using a Monte Carlo SPICE (Simulation Program with Integrated Circuit Emphasis) simulation. The variations of the IC are L and VTO variations. An evaluation method is used to evaluate the effects of the variations by modeling it using a normal (Gaussian) distribution. The simulation results show that the IC may be detected as a defective IC caused by the variations based on large supply currents flow to it.

Keywords: Process Variations, High-Speed Complementary Metal Oxide Semiconductor Integrated Circuit, Monte Carlo, Normal Distribution

#### 1. Introduction

A HCMOS (High-Speed Complementary Metal Oxide Semiconductor) IC (Integrated Circuit) 2 a family of CMOS (Complementary Metal Oxide Semiconductor) ICs [1]. Thus, it consists of p-type and n-type MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) [2]. However, it has lower power dissipation than that one CMOS ICs.

A CMOS IC is identified by six masks, i.e., n-well, polysilicon, n+ diffusion, p+ diffusion, contacts, and metal. There are many processes required to fabricate the CMOS IC by creating the masks, such as lithography, dopant, and others [3]. Each process may generate variations during IC fabrication caused by operating conditions [4]. Unfortunately, the process variations may affect performances of the IC [5].

Process variations of the IC are channel length L, threshold voltage VTO, and oxide thickness TOX variations [6]. However, the TOX variation causes minor effects compared to others [7]. Thus, the effects of the L and the VTO variations should be evaluated.

The L variation may be triggered by lithography limitation [8]. On the other hand, the number of dopant atoms may cause the VTO variation [9]. Both of the L and the VTO variations may cause the IC experiences error in its operation [10].

A faulty CMOS IC was detected by an IDDQ testing [11]. The faulty might be caused by an open defect of a metal in an input gate. The testing was based on measuring a quiescent supply current IDDQ of the IC. The testing shows that the large quiescent supply current IDDQ will flow to the IC when the open defect is detected. By using this phenomenon, an IC is detected as a faulty by flowing a large quiescent 5 pply current IDDQ to it.

In this paper, a Monte Carlo SPICE (Simulation Program with Integrated Circuit Emphasis) simulation is proposed to evaluate the effects of L and VTO variations in a HCMOS IC. The variations are modeled by a normal (Gaussian) distribution; afterwards, they are examined using the SPICE simulation of LTSpiceIV. The simulation results are then compared to the faulty IC [11]. A HCMOS IC may be detected as a defective IC caused by L and VTO variations based on large quiescent supply currents IDDQ flow to it.

#### 2. EvaBation Method

In order to evaluate the effects of L and the VTO variations of a HCMOS IC, the variations are modeled by a normal (Gaussian) distribution [12]. The distribution is depicted in Figure 1. As shown in Figure 1,  $\mu$  and  $\sigma$  are a mean and a standard deviation respectively.

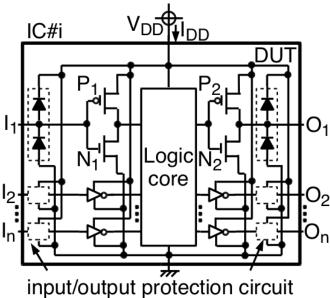

A HCMOS IC design in Figure 2, IC#i, is made to evaluate the effects of the variations. The design consists of input protection circuits, input inverters, a logic core, output inverters, and output protection circuits.

Widianto, W., Syafaah, L., & Nurhadi, N. (2017). Effects of Process Variations in a HCMOS IC using a Monte Carlo SPICE Simulation. Kinetik: Game Technology, Information System, Computer Network, Computing, Electronics, and Control, 3(1). http://dx.doi.org/10.22219/kinetik.v3i1.437 Paper submitted on August 10, 2017; Revision on October 30, 2017; Received November 13, 2017

Figure 1. Gaussian Distribution

Figure 2. Design of Evaluation IC

As shown in Figure 2, a supply voltage  $V_{DD}$ , a supply current  $I_{DD}$ , input pins  $I_1$  to  $I_2$ , and output pins  $O_1$  to  $O_n$  are provided to the design. The core may be inserted by INVERTER, NAND, and NOR gates.

The standard deviation of the L and the VTO of the IC design are modeled by using Equations 1 and 2. By using these equations, the L and the VTO variations of the IC design are determined by Equations 3 and 4 subsequently.

$$\sigma_L = (n\% \cdot L) \tag{1}$$

$$\sigma_{VTO} = (n\% \cdot VTO)$$

(2)

$$VTO_n = VTO + gauss (\sigma_{VTO})$$

(3)

$$L_n = L + gauss(\sigma_L)$$

(4)

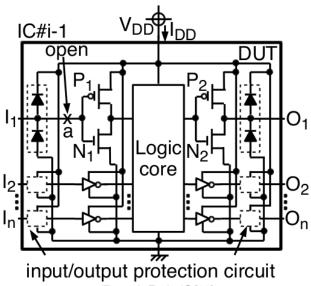

Moreover, an evaluation method is proposed to evaluate the effects of the L and the VTO variation in *IC#i* by using a Monte Carlo SPICE simulation for measuring a quiescent supply current IDDQ. The simulation results are compared to the proposed IDDQ testing result [11] of a faulty IC. The faulty IC is illustrated in Figure 3, caused by an open defect inside it. The large quiescent supply current IDDQ will flow to the IC caused by the open defect.

Tolerance ranges of the L and the VTO variations in IC#i are determined by comparing their quiescent supply current IDDQ results to the IDDQ testing result [11]. IC#i may be detected

KINETIK Vol. 3, No. 1, February 2018: 11-16

as defective IC by flowing the quiescent supply currents IDDQ being equal or larger than [11]. Hence, the maximum tolerance ranges of the L and the VTO variations are determined by the quiescent supply current IDDQ results are lower than [11].

#### 3. Results ad Discussions

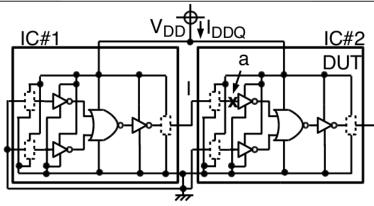

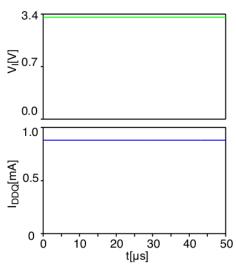

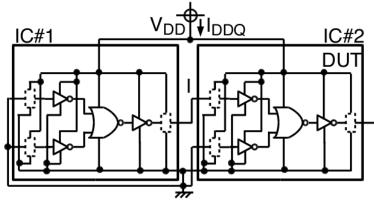

A simulation circuit was made to detect a faulty CMOS IC by using an IDDQ testing [11]. The circuit is presented in Figure 4, made by two ICs, IC#1 and IC#2. The IC#2 is a DUT (Device Under Test) of the faulty IC. The faulty is caused by an open defect denoted as "a" occurring inside the IC#2.

Figure 3. Faulty IC [11]

Both the ICs are designed using a SPICE Netlist Library distributed by NXP Co. Ltd. The ICs are an identical to a HCMOS IC design as shown in Figure 2. A NOR gate is used as a logic core in each the IC, so the functional ICs are as NAND gates.

A supply voltage  $V_{DD}$  is provided to the ICs by 3.3  $\overline{\text{V}}$ . The open defect is made by inserting a resistor 1 T $\Omega$  to a. The testing is based on measuring a quiescent supply current IDDQ of the ICs. The simulation result in Figure 5 shows large quiescent supply current IDDQ flowing to the ICs causing open defect. By using this phenomenon, an IC is detected as a faulty by flowing a large rescent supply current IDDQ to it.

In order to evaluate the effects of L and VTO variations in a HCMOS IC, the simulation of circuit one is proposed and shown in Figure 6. The circuit is identical to the circuit in Figure 4; however, there is no detected defect. L and VTO variations of the circuit are modeled by modifying the SPICE Netlist Library using Equations 1 to 4.

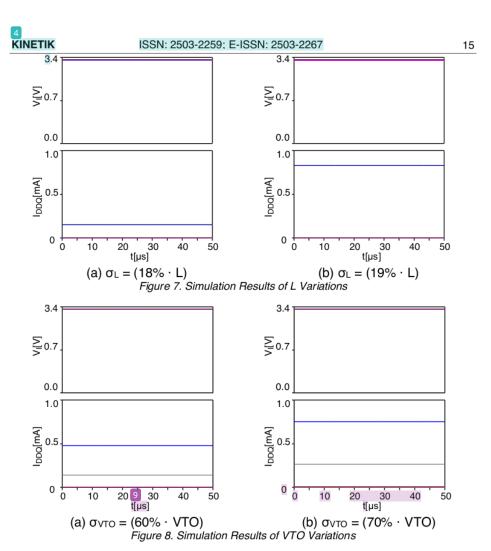

Furthermore, the circuit in Figure 6 is simulated by a Monte Carlo SPICE simulation of LTSpice IV. The quiescent supply currents  $I_{DDQ}$  are measured to evaluate the effects of L and VTO variations. The  $I_{DDQ}$  values are compared to the proposed  $I_{DDQ}$  values [11]. When the  $I_{DDQ}$  values are equal or larger than them, the IC is detected as a faulty IC. The simulation results of  $\underline{L}$  and VTO variations are shown in Figures 7 and 8 respectively.

As shown in Figure 7(a),  $I_{DDQ}$  values are less than 0.75 mA by using  $\sigma_L = (18\% \cdot L)$ . On the other hand, in Figure 7(b), with  $\sigma_L = (19\% \cdot L)$ ,  $I_{DDQ}$  values are larger than 0.75 mA or equal to the  $I_{DDQ}$  values [10]. Therefore, a maximum standard deviation of L variations is  $\sigma_L = (18\% \cdot L)$ .

Moreover, in Figure 8 (a), by using  $\sigma_{VTO}$  = (60% · VTO),  $I_{DDQ}$  values are less than 0.75 mA. However, in Figure 8(b),  $I_{DDQ}$  values are larger than 0.75 mA or equal to the  $I_{DDQ}$  values [11] with  $\sigma_{VTO}$  = (70% · L). Moreover,  $\sigma_{VTO}$  = (60% · VTO) is a maximum standard deviation of the *VTO* variations.

Figure 4. Simulation Circuit of Faulty IC

Figure 5. Simulation Circuit of Faulty IC

Figure 6. Simulation Circuit of Process Variation

#### 4. Conclusion

The effects of process variations in a HCMOS IC are evaluated by using a Monte Carlo SPICE simulation of LTSpice IV. The process variations are L and VTO variations and modeled by a Gaussian distribution.

The simulation results show that maximum standard deviations of L and VTO variations are  $\sigma_L = (18\% \cdot L)$  and  $\sigma_{VTO} = (60\% \cdot VTO)$  respectively. Furthermore, it means that the maximum tolerance range of L variation is  $L \pm (18\% \cdot L)$ . However, VTO  $\pm (60\% \cdot VTO)$  is the maximum tolerance range of VTO variation.

#### 5. Notations

n : counting number

$\sigma_L$  : standard deviation of L variation  $\sigma_{VTO}$ : standard deviation of VTO variation

#### Acknowledgment

This work is supported by Universitas Muhammadiyah Malang under grant of P2I No. 1322/SK-BAA/XII/2016

#### References

- [1] K. Bernstein, et al., "High Speed CMOS Design Style", Kluwer Academic Publishers, 1999.

- [2] R.C. Jaeger and T.N. Blalock, "Microelectronic Circuit Design, Fourth Edition", McGraw-Hill Companies, Inc., 2011.

- [3] N.H.E. Weste and D.M. Harris, "CMOS VLSI Design, A Systems and Circuits Perspective, Fouth Edition", Addison-Wesley, 2011.

- [4] M. Onabajo and J. Silva-Martinez, "Analog Circuit Design for Process Variation-Resilient System-on-a-Chip", Springer, 2012.

- [5] S. Reda and S.R. Nassif, "Analzing the Impact of Process Variation on Parametic Measurements: Novel Model and Applications", Design Automation and Test in Europe, Pp. 375-380, 2009.

- [6] V. Mehrotra, S.L. Sam, D. Boning, A. Chandrakasan, R. Vallishaye, and S. Nassif, "A Methodology for Modeling the Effects of Systematic Within-Die Interconnect and Device Variation on Circuit Performance", Proceedings of Design Automation Conference, Pp. 172-175, 2000.

- [7] K.G. Verma and B.K. Kaushik, "Effect of Process Based Oxide Thickness Variation on the Delay of DIL System using Monte Carlo Analysis", International Journal of Recent Trends in Engineering and Technology, Vol. 3 No. 4, Pp. 28-31, 2010.

- [8] M. Wirnshofer, "Variation Aware Adaptive Voltage Scaling for Digital CMOS Circuits", Springer, 2013.

- [9] N. Drego, A. Chandrakasan, and D. Boning, "A Test-Structure to Efficiently Study Threshold-Voltage Variation in Large MOSFET Arrays", International Symposium on Quality Electronic Design (ISQED), Pp. 281-286, 2007.

- [10] A. Beg, A. Elchouemi, and R. Beg, "Effect of Channel Lengthening and Threshold Voltage Variation on a Nanometric Gate's Delay and Power", International Conference on COmputer Design (CDES), Pp. 55-59, 2012.

- [11] Widianto, Lailis Syafaah, Nurhadi, "Open Defect Detection of CMOS ICs using IDDQ Testing", National Seminar on Technology and Engineering (SENTRA), Pp. 188-190, 2016

- [12] J.L. Devore, "Probability and Statistics for Engineering and the Sceiences, Eight Edition", Cengage Learning, 2012.

## Effects of Process Variations in a HCMOS IC using a Monte Carlo SPICE Simulation

| ORIGIN                 | IALITY REPORT                                                                        |                                  |                 |                      |

|------------------------|--------------------------------------------------------------------------------------|----------------------------------|-----------------|----------------------|

| 9%<br>SIMILARITY INDEX |                                                                                      | <b>7</b> % INTERNET SOURCES      | 2% PUBLICATIONS | 3%<br>STUDENT PAPERS |

| PRIMAI                 | RY SOURCES                                                                           |                                  |                 |                      |

| 1                      | Submitt<br>Student Pape                                                              | ed to Universita<br><sup>r</sup> | s Islam Indon   | esia 2%              |

| 2                      | www.coursehero.com Internet Source                                                   |                                  |                 |                      |

| 3                      | Lecture Notes in Computer Science, 2004.  Publication                                |                                  |                 |                      |

| 4                      | downloa<br>Internet Sour                                                             | ad.garuda.kemo                   | likbud.go.id    | 1 %                  |

| 5                      | koreasc<br>Internet Sour                                                             | ience.or.kr                      |                 | 1 %                  |

| 6                      | Submitted to Universitas Brawijaya Student Paper                                     |                                  |                 |                      |

| 7                      | m.moam.info Internet Source                                                          |                                  |                 |                      |

| 8                      | fr.slideserve.com Internet Source                                                    |                                  |                 |                      |

| 9                      | Sebastian Mehl, David P. DiVincenzo. "Noise analysis of qubits implemented in triple |                                  |                 |                      |

# quantum dot systems in a Davies master equation approach", Physical Review B, 2013

< 1%

Publication

Exclude quotes On Exclude matches

Exclude bibliography On

## **Digital Receipt**

This receipt acknowledges that Turnitin received your paper. Below you will find the receipt information regarding your submission.

The first page of your submissions is displayed below.

Artikel 2 Submission author:

Lailis Syafaah 2 Assignment title:

Submission title: Effects of Process Variations in a HCMOS IC using a Monte C...

Effects\_of\_Process\_Variations\_in\_a\_HCMOS\_IC\_using\_a\_Mont... File name:

442.13K File size:

Page count: 6

Word count: 2,077

Character count: 9,945

Submission date: 17-Jan-2024 11:10AM (UTC+0700)

Submission ID: 2272326819

UNETIK, Vol. 3, No. 1, February 2018, Pp. 11-16 SSS 2003-2028 SSS 2003-2029 Effects of Process Variations in a HCMOS IC using a Monte Carlo SPICE Simulation