# BAB II

## Widianto Syafaah

🗐 Syafaah Fauziah Zulfatman

- Teknik Elektro

- University of Muhammadiyah Malang

## **Document Details**

Submission ID trn:oid:::1:2999598487

Submission Date Sep 6, 2024, 10:04 AM GMT+7

Download Date Sep 6, 2024, 10:05 AM GMT+7

File Name

$ianto\_Syafaah\_Nurhadi\_-OPEN\_DEFECT\_DETECTIONS\_CMOS\_ICS\_IDDQ.pdf$

File Size

442.8 KB

3 Pages

1,068 Words

4,802 Characters

## **16% Overall Similarity**

The combined total of all matches, including overlapping sources, for each database.

## Filtered from the Report

- Bibliography

- Quoted Text

#### Exclusions

11 Excluded Sources

### **Match Groups**

**Top Sources**

Internet sources

Submitted works (Student Papers)

Publications

5%

11%

5%

- 14 Not Cited or Quoted 16% Matches with neither in-text citation nor quotation marks

- **0** Missing Quotations 0% Matches that are still very similar to source material

- = 0 Missing Citation 0% Matches that have quotation marks, but no in-text citation

- O Cited and Quoted 0%

Matches with in-text citation present, but no quotation marks

## **Integrity Flags**

#### 1 Integrity Flag for Review

Hidden Text 0 suspect characters on 3 pages Text is altered to blend into the white background of the document. Our system's algorithms look deeply at a document for any inconsistencies that would set it apart from a normal submission. If we notice something strange, we flag it for you to review.

A Flag is not necessarily an indicator of a problem. However, we'd recommend you focus your attention there for further review.

## Match Groups

Page 3 of 6 - Integrity Overview

न turnitin

| Match Groups                                                                                                     | Top Sources                                                      |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 14 Not Cited or Quoted 16%<br>Matches with neither in-text citation nor quotation marks                          | <ul><li>5%  Thternet sources</li><li>11%  Dublications</li></ul> |

| <ul> <li>Missing Quotations 0%</li> <li>Matches that are still very similar to source material</li> </ul>        | 5% 💄 Submitted works (Student Papers)                            |

| O Missing Citation 0%<br>Matches that have quotation marks, but no in-text citation                              |                                                                  |

| <ul> <li>O Cited and Quoted 0%</li> <li>Matches with in-text citation present, but no quotation marks</li> </ul> |                                                                  |

| <b>Top Sources</b><br>The sources with the highest number of matches within the submission. Ov                   | verlapping sources will not be displayed.                        |

| 1 Student papers                                                                  |    |

|-----------------------------------------------------------------------------------|----|

| Universitas Islam Indonesia                                                       | 3% |

|                                                                                   |    |

| 2 Publication                                                                     |    |

| Widianto, Robert Lis. "Delay analysis in HCMOS logic ICs", AIP Publishing, 2022   | 3% |

|                                                                                   |    |

| 3 Publication                                                                     |    |

| T. Tamesada. "Electric Field for Detecting Open Leads in CMOS Logic Circuits by S | 3% |

|                                                                                   |    |

| 4 Publication                                                                     |    |

| Konishi, Tomoaki, Hiroyuki Yotsuyanagi, and Masaki Hashizume. "A built-in test ci | 3% |

|                                                                                   |    |

| 5 Publication                                                                     |    |

| Hashizume, Masaki, Shoichi Umezu, Hiroyuki Yotsuyanagi, and Shyue-Kung Lu. "      | 2% |

|                                                                                   |    |

| 6 Internet                                                                        |    |

| www.coursehero.com                                                                | 2% |

## OPEN DEFECT DETECTIONS OF CMOS ICS BY USING I<sub>DDQ</sub> TESTING

Widianto, Lailis Syafaah, Nurhadi

Electric Departemen, Engineering Favulty, Muhammadiyah University of Malang

Contact Person: Widianto Jl. Raya Tlogomas 246 Malang, Telp. 0341-464318, Fax.0341-460782 E-mail: widianto@umm.ac.id

### Abstract

An  $I_{DDQ}$  testing is proposed to detect an open defect at an input gate in a CMOS IC. The testing is based on measuring a quiescent supply current  $I_{DDQ}$  on the IC. When the open defect occurs at the input gate, the large  $I_{DDQ}$  will flow to the IC regardless test input vectors which generate to it. On the other hand, in the defect-free IC, the large  $I_{DDQ}$  does not flow to the IC. The testing is implemented in the CMOS IC designed by a Spice net list library of NXP Co. Ltd and is examined using a Spice simulation. Simulation results show that the open defect can be detected by the  $I_{DDQ}$  testing.

Keywords: IDDO testing, open defect, input gate, CMOS IC

### **1. Introduction**

Recently, the density and the complexity of CMOS (complementary metal oxide semiconductor) ICs (integrated circuits) increase significantly [1]. It makes a challenge to test the ICs before shipping to customers, where open and short defects could occur at its input gates.

The short defects are bridging between two or more metal lines in the ICs. Most the shorts are caused by extra conducting materials [2].  $I_{DDQ}$  testing technique has been proposed to detect the short defects [3]. The defects can be detected by measuring a large quiescent supply current  $I_{DDQ}$  flows in the ICs.

The open defects are opens at metal lines. They are caused by the increasing number contacts and vias [4]. The defects can be detected by the  $I_{DDQ}$  testing [5]. However, test input vectors should be determined earlier to detect the defects.

In this paper, an  $I_{DDQ}$  testing is proposed to detect an open defect at an input gate in a CMOS IC regardless generated test input vectors. Analysis results were denoted to evaluate the feasibility of the testing in detecting the defect.

## 2. IDDQ Testing

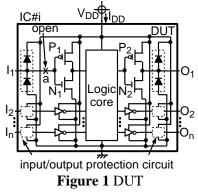

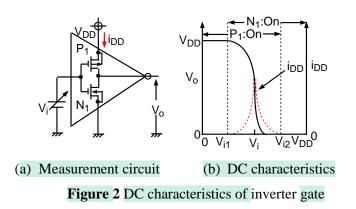

A testable DUT (device under test) IC is made of the proposed  $I_{DDQ}$  testing shown in Fig. 1. As shown in Fig. 1, the IC is made of input protection circuits, inverters, a logic core, and output protection circuits. A targeted open defect is denoted by "a".

Electrical characteristics of the inverter gate which is between the input protection circuit and the logic core are shown in Fig. 2. As shown in Fig. 2(b), when an input voltage of the gate Vi is a H or a L level, supply current  $i_{DD}$  of almost zero will flow into the gate. On the other hand, if Vi is in a

range specified by Eq. (1), large  $i_{DD}$  will flow, since both a pMOS  $P_1$  and an nMOS  $N_1$  in the gate turn on.

$$Vi_1 \le Vi \le Vi_2 \tag{1}$$

When an open defect occurs at *a*, a large quiescent supply current  $I_{DDQ}$  flows to the IC, regardless either a *H* or a *L* level is provided to an input of the IC  $I_1$ , since the input voltage of the inverter is the range specified Eq. (1). However the  $I_{DDQ}$  is almost zero flows in the defect-free IC, when the input voltage of the inverter is either the *H* or the *L* level.

## **3. Result and Discussion**

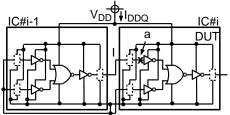

A simulation circuit is made to evaluate the feasibility of the proposed  $I_{DDQ}$  testing as shown in Fig. 3. The circuit is made of two ICs, IC#i-1 and IC#i. Each of the ICs is designed using a Spice netlist library distributed by NXP. CO. Ltd. A targeted open defect is denoted by "a" in the DUT of IC#i.

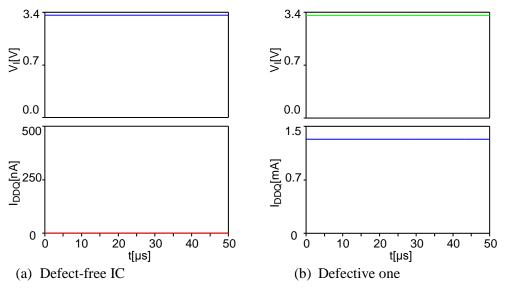

The power supply voltage 3.3 V and a resistor 1  $T\Omega$  are provided to  $V_{DD}$  and *a*, respectively. The simulation results are summarized in Fig. 4. As shown in Fig. 4, when an open defect occurs at *a*, a quiescent supply current  $I_{DDQ}$  flows to the circuit.

Figure 3 Simulation circuit

A simulation circuit is made to evaluate the feasibility of the proposed  $I_{DDQ}$  testing as shown in Fig. 3. The circuit is made of two ICs, IC#i-1 and IC#i. Each of the ICs is designed using a Spice netlist library distributed by NXP. CO. Ltd. A targeted open defect is denoted by "a" in the DUT of IC#i.

## 4. Conclusion

An  $I_{DDQ}$  testing was proposed to detect an open defect in a CMOS IC. The feasibility of the testing was evaluated by a Spice simulation. The simulation results show that the open defect can be detected by the large  $I_{DDQ}$  flows to the IC. It remains a future work, the open defect should be located by the testing.

Figure 4 Simulation results

## Referensi

- [1] Neil HEW, David MH. CMOS VLSI Design. A Circuits and Systems Perspective. Fourth Edition. Addison Wesley. 2011.

- [2] Ferguson, FJ and Shen, JP, A CMOS Fault Extractor for Inductive Fault Analysis. *IEEE Trans. on Computer-Aided Design*, 1988;7(11): 1181–1194.

- [3] Rajsuman R. Iddq Testing for CMOS VLSI. Proceeding of the IEEE. 2000;88(4): 544-568.

- [4] Thompson KM. Intel and The Myths of Test. *IEEE Design and Test Computers*.1996;13(1): 79-81.

- [5] Michinisi H, et.al. CMOS Floating Gate Defect Detection Using IDDQ Test with DC Power Supply Superposed by AC Component. Proceeding of the 11<sup>th</sup> Asian Test Symposium. 2002: 417-422.